# Extending the C/C++ Memory Model with Inline Assembly

joint work with presented by on the Ori Lahav, Viktor Vafeiadis, and Azalea Raad Paulo Emílio de Vilhena 23rd of October, 2024

#### Problem.

Specify the semantics of inline x86 assembly in a concurrent setting with shared memory.

### Motivation.

*Inline assembly* allows one to insert snippets of x86 assembly in C/C++ code.

### Applications of inline assembly include

- Writing *efficient code* directly in x86 assembly

- Access to *instructions* that *do not exist* in C/C++

- Customizing call conventions

### Challenge.

Architecture (x86) and source language (C/C++) follow incompatible concurrency models.

#### Problem.

*Specify* the semantics of *inline* x86 *assembly* in a *concurrent* setting with *shared memory*.

### Motivation.

*Inline assembly* allows one to insert snippets of x86 assembly in C/C++ code.

### Applications of inline assembly include

- Writing efficient code directly in x86 assembly

- Access to *instructions* that *do not exist* in C/C++

- Customizing call conventions

```

int src = 42, dst = 0;

// non-temporal store

asm volatile (

"movnti %[src], %[dst]"

: [dst] "=m" (dst)

: [src] "r" (src)

: "memory");

assert(dst == 42);

```

### Challenge.

Architecture (x86) and source language (C/C++) follow incompatible concurrency models.

#### Problem.

Specify the semantics of *inline x86 assembly* in a *concurrent* setting with *shared memory*.

### Motivation.

*Inline assembly* allows one to insert snippets of x86 assembly in C/C++ code.

### Applications of inline assembly include

- Writing *efficient code* directly in x86 *assembly*

- Access to *instructions* that *do not exist* in C/C++

- Customizing call conventions

```

int src = 42, dst = 0;

// non-temporal store

asm volatile (

"movnti %[src], %[dst]"

: [dst] "=m" (dst)

: [src] "r" (src)

: "memory");

assert(dst == 42);

```

### Challenge.

Architecture (x86) and source language (C/C++) follow incompatible concurrency models.

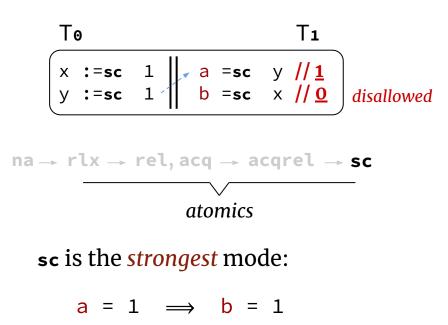

RC11[Lahav et al.] is a model for C/C++.

| Τo     |   |       |   | T1 |

|--------|---|-------|---|----|

| x :=sc | 1 | a =sc | у |    |

| y :=sc | 1 | b =sc | х |    |

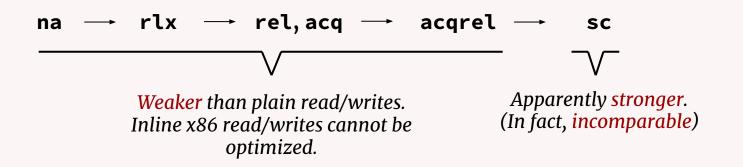

$$na \rightarrow rlx \rightarrow rel, acq \rightarrow acqrel \rightarrow sc$$

atomics

| Тө   |   |       | Τı |

|------|---|-------|----|

| x := | 1 | a = y |    |

| y := | 1 | b = x |    |

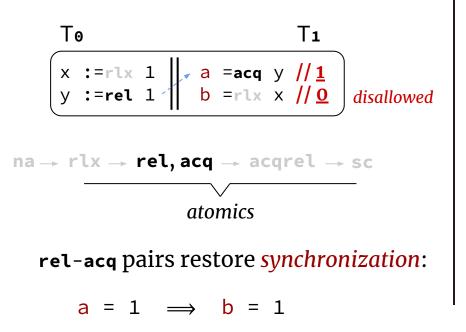

RC11[Lahav et al.] is a model for C/C++.

| Τø   |   |       | Τı |

|------|---|-------|----|

| x := | 1 | a = y |    |

| y := | 1 | b = x |    |

RC11[Lahav et al.] is a model for C/C++.

ToT1

$$x := rlx 1$$

$a = rlx y //1$  $y := rlx 1$  $b = rlx x //0$

$$na \rightarrow rlx \rightarrow rel, acq \rightarrow acqrel \rightarrow sc$$

atomics

rlx is the *weakest* atomic mode:

$$a = 1 \implies b = 1$$

| Τo   |   |       | Τı |

|------|---|-------|----|

| x := | 1 | a = y |    |

| y := | 1 | b = x |    |

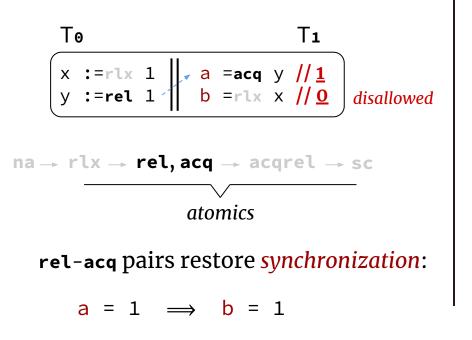

RC11[Lahav et al.] is a model for C/C++.

| Τø   |   |       | Τı |

|------|---|-------|----|

| x := | 1 | a = y |    |

| y := | 1 | b = x |    |

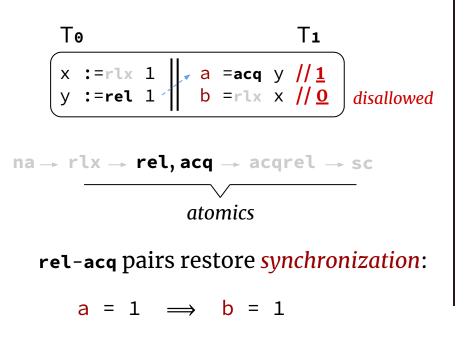

*RC*11[Lahav et al.] is a model for *C*/*C*++.

*Ex86* [<u>Raad et al.</u>] is a model for *x86 assembly*.

| Тө           |        | T1                                                                                              |

|--------------|--------|-------------------------------------------------------------------------------------------------|

| x :=<br>y := | 1<br>1 | $ \begin{vmatrix} a &= y // \underline{1} \\ b &= x // \underline{0} \end{vmatrix} $ disallowed |

In x86, plain reads and writes follow TSO: Only write-read pairs can be reordered.

$$a = 1 \implies b = 1$$

*RC*11[Lahav et al.] is a model for *C*/*C*++.

*Ex86* [<u>Raad et al.</u>] is a model for *x86 assembly*.

| Тө             |        | T1                                                                   |

|----------------|--------|----------------------------------------------------------------------|

| x :=<br>y :=nt | 1<br>1 | $ \begin{vmatrix} a &= y // 1 \\ b &= x // 0 \end{vmatrix} allowed $ |

*Non-temporal stores* bypass *the cache*: They can be *reordered* with other *writes*.

$$a = 1 \implies b = 1$$

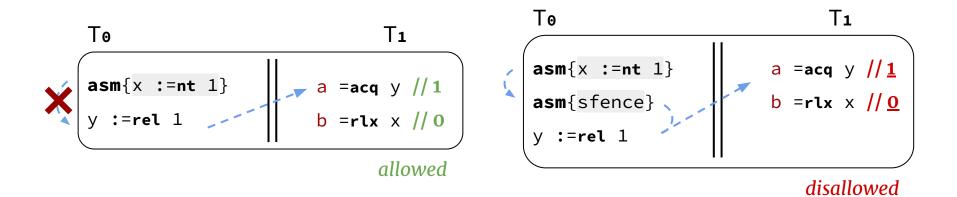

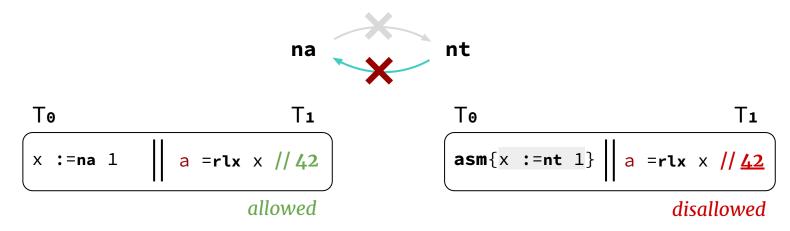

# Challenges – Non-temporal stores

Consequence to C/C++ memory model: **nt** stores *break* **rel**-**acq** *synchronization*!

To T1

asm{x :=nt 1}

y :=rel 1

$$\rightarrow$$

b = 1

To T1

a = acq y // 1

b =rlx x // 0

#### **Challenges:**

- *Relax RC11* in such a way that this behavior is *allowed*.

- Suggest how to restore synchronization (e.g. through x86's store fences).

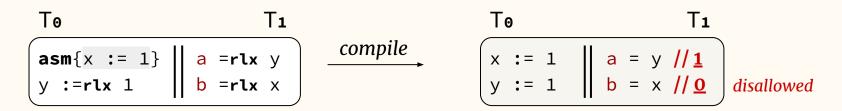

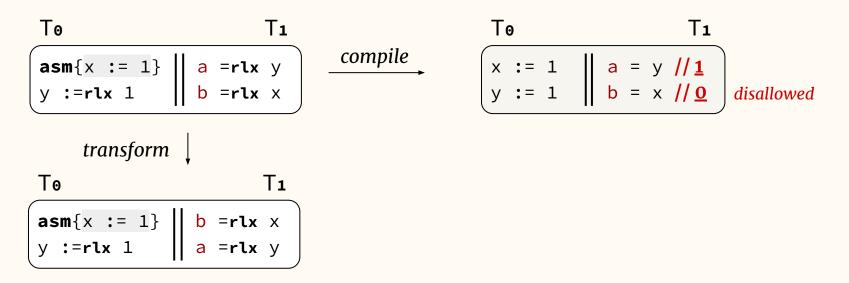

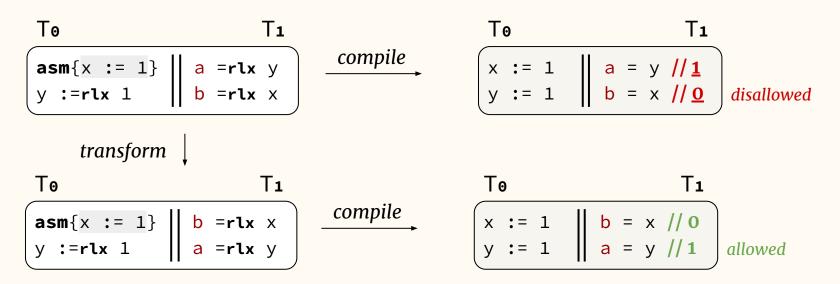

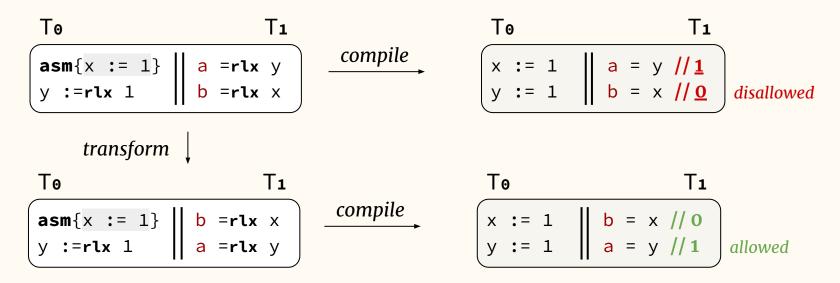

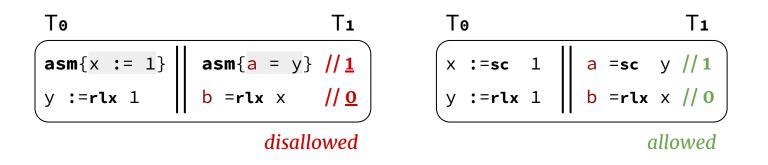

# Challenges - Compiler optimizations

*Compiler optimizations* introduce behaviors that violate *Ex86 consistency*.

# **Challenges – Compiler optimizations**

#### *Compiler optimizations* introduce behaviors that violate *Ex86 consistency*.

# **Challenges – Compiler optimizations**

#### *Compiler optimizations* introduce behaviors that violate *Ex86 consistency*.

# **Challenges – Compiler optimizations**

#### *Compiler optimizations* introduce behaviors that violate *Ex86 consistency*.

Challenge: Enforce Ex86 consistency in a way that does not break optimizations.

# Challenges – Access modes are unfit for inline assembly

It is *not* possible to model *inline-assembly accesses* using *RC11 access modes*:

#### **Challenges:**

- Invent new access modes for inline-assembly accesses.

- *Discover* how the new access modes *relate* to the existing *RC11* ones.

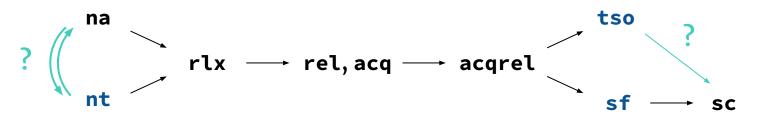

We introduce **RC11**<sup>Ex86</sup>, an *extended model* for C/C++ with inline x86 assembly.

**RC11**<sup>Ex86</sup> handles the three aforementioned challenges:

1. *Non-temporal stores* do *not* enforce *synchronization* unless followed by a (sufficiently strong) *barrier*.

### We introduce **RC11**<sup>Ex86</sup>, an *extended model* for C/C++ with inline x86 assembly.

### **RC11**<sup>Ex86</sup> handles the three aforementioned challenges:

1. Non-temporal stores do not enforce synchronization unless followed by a (sufficiently strong) barrier.

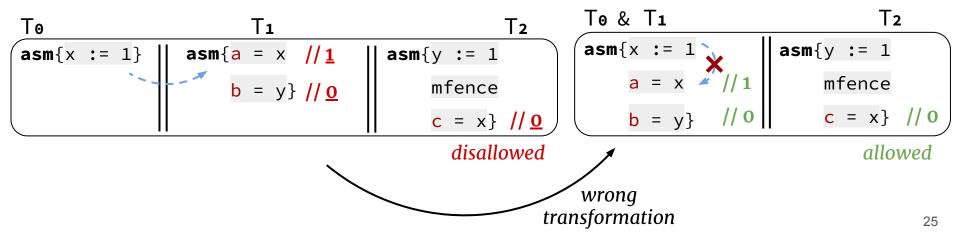

2. Threads must use *inline assembly* to abide by *Ex86 consistency*. *Compiler optimizations* can be applied to C/C++ portions of code.

| Тө              | T1                     | Τ2       |

|-----------------|------------------------|----------|

| $asm\{x := 1\}$ | asm{a = y} // <u>1</u> | C =rlx y |

| y :=rlx 1       | b =rlx × // <u>0</u>   | d =rlx x |

### We introduce **RC11**<sup>Ex86</sup>, an *extended model* for C/C++ with inline x86 assembly.

### **RC11**<sup>Ex86</sup> handles the three aforementioned challenges:

1. Non-temporal stores do not enforce synchronization unless followed by a (sufficiently strong) barrier.

2. Threads must use *inline assembly* to abide by *Ex86 consistency*. *Compiler optimizations* can be applied to C/C++ portions of code.

| То              | Tı                        | T2            |

|-----------------|---------------------------|---------------|

| $asm\{x := 1\}$ | asm{ <mark>a = y</mark> } | c =rlx y //1  |

| y :=rlx 1       | b =rlx ×                  | d =rlx × // 0 |

|                 |                           | allowed       |

### We introduce **RC11**<sup>Ex86</sup>, an *extended model* for C/C++ with inline x86 assembly.

### **RC11**<sup>Ex86</sup> handles the three aforementioned challenges:

- 1. Non-temporal stores do not enforce synchronization unless followed by a (sufficiently strong) barrier.

- 2. Threads must use *inline assembly* to abide by *Ex86 consistency*. *Compiler optimizations* can be applied to C/C++ portions of code.

- 3. Introduction of new access modes for non-temporal stores (nt), plain reads/writes (tso), and store fences (sf).

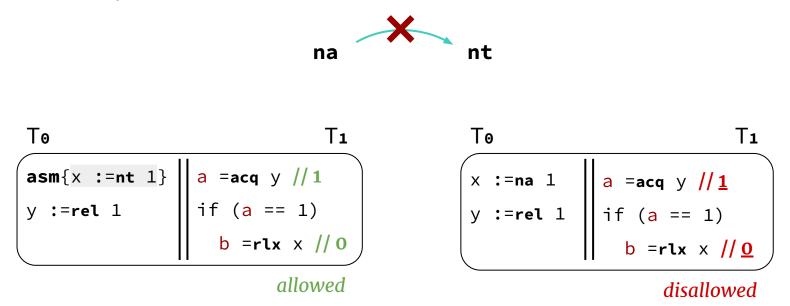

Non-temporal (nt) stores can be weaker than non-atomic (na) accesses.

Conversely, *non-atomic* (**na**) accesses can be weaker than *non-temporal* (**nt**) stores.

Why races on inline-assembly accesses are not UB?

There are *multiple reasons*, we cite *two*:

- Programs fully written in *inline assembly* would *not* abide by x86 consistency.

- Inline assembly is not optimized like **na** accesses.

The semantics of **sc** *accesses* can be *weaker* than *TSO*.

tso → sc

### **RC11<sup>Ex86</sup> – Properties**

**Extension of RC11.** Programs without inline assembly have RC11 semantics:

$$P \in RC_{11} \quad \Rightarrow \quad \left[ \begin{array}{c} P \end{array} \right]_{RC_{11}^{Ex86}} = \left[ \begin{array}{c} P \end{array} \right]_{RC_{11}}$$

Extension of Ex86. Programs fully written in inline assembly have Ex86 semantics:

$$P \in Ex86 \qquad \Rightarrow \qquad \left[ \left[ \operatorname{asm}\{P\} \right] \right]_{RC11^{Ex86}} = \left[ \left[ P \right] \right]_{Ex86}$$

Data-race freedom. Data-race-free programs have SC semantics:

$$P \text{ has sc-only races} \quad \Rightarrow \quad \left[ \begin{array}{c} P \end{array} \right]_{\mathbf{RC11}^{\mathbf{E}\times 86}} = \quad \left[ \begin{array}{c} P \end{array} \right]_{\mathbf{SC}}$$

# **RC11<sup>Ex86</sup> – Properties**

We show *correctness of compilation* with respect to RC11<sup>Ex86</sup> and Ex86.

Moreover, sound compiler optimizations in RC11 are also sound in RC11<sup>Ex86</sup>; There is however one caveat: In RC11<sup>Ex86</sup>, sequentialization is not sound in general.

In x86, reading an *external* write enforces synchronization, whereas reading an *internal* write does *not*.

# Conclusion

*Inline assembly* is an important tool that is *not* handled by the *RC11 model*.

Many challenges exist.

- Non-temporal stores break rel-acq synchronization.

- *Ex86-consistency* is incompatible with many compiler optimizations.

- Inline-assembly accesses cannot be modeled with RC11 access modes.

We introduce **RC11<sup>Ex86</sup>**, an *extended model* for C/C++ with inline x86 assembly.

- One can **restore rel-acq** synchronization through barriers, such as store fences.

- The scope of Ex86-consistency is limited to threads with inline assembly. (Compiler optimizations can be applied to C/C++ portions of code.)

- Inline-assembly accesses are modeled using new accesses modes.

The **RC11**<sup>Ex86</sup> model enjoys many properties

- Extension of RC11 and Ex86

- Data-race freedom

- Correctness of compilation and compiler optimizations

# Questions